doi:10. 19306/j. cnki. 2095-8110. 2019. 02. 012

# 合理运用 SI 技术快速收敛高速数字电路设计

贾明福,宋舒雯,王 宁,袁 寰

(北京自动化控制设备研究所,北京 100074)

摘 要:随着数字电路集成度和工作频率的不断提高,信号完整性(Signal Integrity, SI)问题在产品研制过程中越来越突出。以惯导系统中的某导航计算机为例,针对故障信号回路,使用仿真软件对其 SDRAM 时钟信号进行信号完整性仿真,并进行优化设计。通过对比优化前和优化后的仿真与测量结果,验证了由于端接参数不匹配造成 SDRAM 时钟信号的非单调性畸变问题。仿真与测量结果表明,在产品研制流程中加入信号完整性仿真环节有利于设计快速收敛,提前规避风险,缩短研发周期,降低设计成本,提高电路产品的可靠性和电磁兼容性。

关键词:数字电路;导航计算机;信号完整性;SDRAM;仿真

中图分类号: U666.1 文献标志码: A

文章编号:2095-8110(2019)02-0081-06

# Rapid Convergence of High-Speed Digital Circuit Design by Using SI Technology

JIA Ming-fu, SONG Shu-wen, WANG Ning, YUAN Huan

(Beijing Institute of Automatic Control Equipment, Beijing 100074, China)

Abstract: With the continuous improvement of the integration level and operating frequency of the digital circuits, the problem of signal integrity (SI) is becoming more and more prominent in product developing. Aiming at the fault signal loop, the signal integrity of SDRAM clock signal of a navigation computer in inertial navigation system is simulated by using simulation software, and the PCB is optimized. By comparing the simulation and measurement results before and after optimization, the nonmonotonic distortion of SDRAM clock signal due to the mismatch of end connection parameters is verified. The simulation and test results show that the simulation of signal integrity in product developing is benefit to accelerating the convergence of design, avoiding the risk in advance, shortening the development cycle, reducing the designing cost and improving the reliability and electromagnetic compatibility of circuit products.

Key words: Digital circuits; Navigation computer; Signal integrity; SDRAM; Simulation

## 0 引言

近年来,随着半导体工艺技术的迅猛发展,晶体管的体积越来越小,芯片的集成度越来越高,单

位芯片内的晶体管数量逐渐增加,数字电路系统朝着高密度和低成本的趋势不断发展<sup>[1]</sup>。与此同时,板级电路信号速度不断提升,串扰、反射、振铃等信号完整性问题日益突出<sup>[2]</sup>。

作为典型的数字电路,惯性捷联导航系统的数字时钟速率也不断提升,由此带来的信号完整性问题已不容忽视。随着捷联惯性技术的不断发展和成熟,惯性导航系统正向着更宽更广的领域发展,如智能炸弹、水下无人制导系统及车载导航等[3-7]。应用领域的拓展和工作速率的提升使得产品的功能性要求和可靠性要求越来越高。各功能电路信号完整性的好坏将直接影响整个惯导系统的可靠性。

在高速数字电路中,若信号完整性问题不能够得到及时解决,将会直接导致信号失真、时序紊乱等,从而造成系统误工作甚至系统崩溃<sup>[8]</sup>。传统的经验设计已无法满足现代半导体产业高速、低电压的技术路线,在电路设计中加入信号完整性仿真成为保证产品可靠性的必需环节<sup>[9]</sup>。

本文以惯性捷联导航系统为例,针对传统经验设计下的某导航计算机 SDRAM 时钟信号异常问题进行了信号完整性仿真与分析,通过对 SDRAM 时钟信号传输路径进行合理的端接设计,得到了符合时序要求的时钟波形。仿真和实验结果表明,将信号完整性仿真融入高速数字电路设计中,有利于指导设计,提高电路可靠性,提前规避风险。

### 1 系统简介

嵌入式导航计算机作为捷联式惯性导航系统的核心设备,主要分为两部分功能电路,分别是信息预处理部分和导航计算部分。其中信息预处理部分主要完成惯性信息的采集及预处理等功能;导航计算部分主要完成惯导系统导航解算以及与外部设备的信息传递[10]。

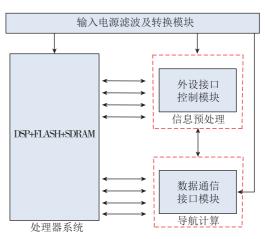

导航计算机硬件电路主要由电源、时钟、处理器、存储器和外围设备组成。其功能电路结构示意图如图 1 所示。处理器系统由 DSP 扩展外部程序存储器 FLASH 和数据存储器 SDRAM 组成。

#### 2 信号完整性概念

信号完整性可以泛指信号的电压、电流在互连结构传输中的信号质量问题,包括噪声、干扰以及由其造成的时序影响等[11]。信号完整性需要保证信号的质量,即要保证信号在驱动端、互连结构上,特别是接收端上的特性,避免产生功能性和稳定性方面的问题[12]。

从传统意义上的数字波形来看,信号质量主要 从过冲、振铃、边沿单调性等几个方面进行评

图 1 导航计算机功能电路结构示意图

Fig. 1 Schematic diagram of circuit structure for navigation computer

判[13-14]。具体定义如下:

1)过冲包括上过冲(Overshoot\_High)和下过冲(Overshoot\_Low) $^{[15]}$ 。上过冲是信号高于信号供电电源电压 $V_{cc}$ 的最高电压,下过冲是信号低于参考地电压 $V_{ss}$ 的最低电压。过大的过冲会导致信号误触发、损坏芯片或者影响其使用寿命。

2)振铃(Ringing)是信号跳变之后的振荡。振铃会使信号的噪声容限减小,过大会造成逻辑错误,而且会使信号的高频分量增加,加剧电磁干扰(Electromagnetic Interference, EMI)问题[16]。

3)边沿单调性(Monotonicity)是指信号上升或下降沿的回沟。对于边沿判决的时钟信号,波形边沿在翻转门限电平处的非单调性可能造成逻辑判断错误[17]。

除此之外,广义的信号质量还包括所有可能引起信号接收、时序、工作稳定性或者电磁干扰方面的不正常现象[18]。因此,在进行数字电路设计时,要合理地运用信号完整性技术手段,反复验证,不断优化,以保证信号的传输质量。

#### 3 信号完整性仿真分析

#### 3.1 信号完整性问题定位

在某惯导系统研制过程中,采用传统经验设计方法设计了一款导航计算机。在系统进行测试的过程中发现处理器通电自检时报用户区程序 CRC校验错误,未完成通电加载。连接仿真器对FLASH区及 SDRAM 区进行测试,多次测试FLASH区并未发现错误,但对 SDRAM 区进行测试时,出现读出和写人数据不相符的情况,所以此

次故障发生的原因为处理器访问 SDRAM 异常。

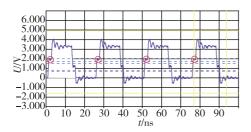

SDRAM 各信号包括时钟信号、复位信号、读写控制信号、地址总线信号以及数据总线信号。使用实验室最高带宽的示波器(2GHz 采样率/500MHz 带宽)对上述信号进行测量,波形未见异常,但在测量 ECLKOUT 信号时 SDRAM 访问故障消失,说明 ECLKOUT 信号完整性可能存在问题,但现有仪器无法准确测量。用仿真软件对 SDRAM 各信号进行信号完整性仿真扫描,除时钟信号网络 ECLKOUT 外其余信号波形均未发现异常。ECLKOUT 仿真波形如图 2 所示。

图 2 ECLKOUT 信号仿真结果

Fig. 2 Simulation result of ECLKOUT signal

由图 2 可以看出,在时钟信号的上升边和下降 沿出现了非单调性问题。对于时钟沿采样的信号, 如果存在非单调性,就可能引起器件的时序错误, 进而导致功能错误,如采样延迟或者在周期内无法 完成采样、出现误触发而产生误码等。

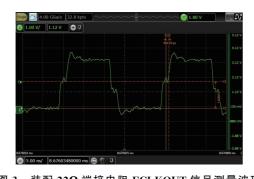

借用安捷伦开放实验室高带宽有源探头示波器测得 SDRAM 时钟输入管脚处信号波形如图 3 所示。

图 3 装配 22Ω 端接电阻 ECLKOUT 信号测量波形 Fig. 3 Measurement waveform of ECLKOUT signal with 22Ω resistance

从图 2 和图 3 中可以看出,信号的仿真结果与 实测结果基本一致,ECLKOUT信号上升沿在 1.82V 附近存在不单调现象,下降沿在 1.31V 附近存在不单调现象。图 4 所示的 SDRAM 数据手册要求高电平判决门限  $V_{IH}$ 为 2V,低电平判决门限  $V_{IL}$ 为 0.8V,即 0.8~2V 为信号判决门限的未定态区间。

DC ELECTRICAL CHARACTERISTICS AND OPERATING CONDITIONS (Notes: 1, 6; notes appear on page 34) (Vob, VobQ = +3.3V ±0.3V)

| PARAMETER/CONDITION                     | SYMBOL    | MIN  | MAX       | UNITS | NOTES |

|-----------------------------------------|-----------|------|-----------|-------|-------|

| SUPPLY VOLTAGE                          | VDD, VDDQ | 3    | 3.6       | ٧     |       |

| INPUT HIGH VOLTAGE: Logic 1; All inputs | Vih       | 2    | VDD + 0.3 | ٧     | 22    |

| INPUT LOW VOLTAGE: Logic 0; All inputs  | VIL       | -0.3 | 0.8       | ٧     | 22    |

图 4 SDRAM 直流电气特性

Fig. 4 DC electrical characteristics of SDRAM

若时钟信号 ECLKOUT 在未定态区间存在不 单调现象,会引起器件采集时钟信号错误,导致器 件读写时序错误或者造成器件内部状态机工作错 误。这样会造成处理器访问 SDRAM 错误,导致处 理器加载异常。

#### 3.2 改进措施

一般来说,在电路板投产前可以通过引入信号完整性仿真,从阻抗匹配、更改 PCB 走线、改变端接拓扑结构等方面改善信号完整性。但在该导航计算机产品已投产,PCB 走线已确定的情况下,最好不改变走线的拓扑结构,选择在已有设计的基础上通过信号完整性仿真优化改变端接电阻的方式进行调整。

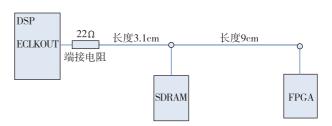

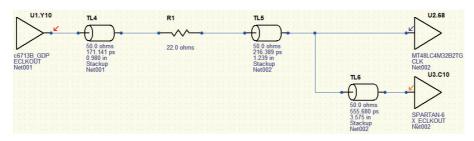

该导航计算机时钟信号 ECLKOUT 的拓扑结构 如图 5 所示。在原版设计中,ECLKOUT 信号经过  $22\Omega$  的串行端接电阻后,驱动 SDRAM 和 FPGA 这 2 个串行负载。其中端接电阻  $R_1$  后端到 SDRAM 的 走线长度为 31.4706mm,SDRAM 到 FPGA 之间的走线长度为 90.805mm。

图 5 ECLKOUT 信号拓扑结构图

Fig. 5 Topology diagram of ECLKOUT signal

根据图 5 拓扑结构及走线长度在仿真软件中建立仿真模型,如图 6 所示。

图 6 ECLKOUT 信号仿真模型

Fig. 6 Simulation model of ECLKOUT signal

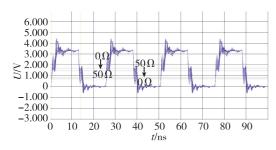

对该模型中  $R_1$  进行参数扫描,选取起始值为  $0\Omega$ ,考虑到阻抗匹配,终值选取  $50\Omega$ ,步进为 4。启动扫描仿真得到 ECLKOUT 波形如图 7 所示。

图 7 0~50Ω 端接电阻 ECLKOUT 信号扫描仿真波形 Fig. 7 Simulation waveform of ECLKOUT signal with 0~50Ω resistance

从图 7 可以看出,改变  $R_1$  阻值上升沿和下降沿不单调现象依然存在,而且阻值越小不单调的重叠区域和过冲越大;但随着阻值的减小,上升沿非单调性的位置不断上升,下降沿非单调性的位置不断下降。从边沿采样的角度来说,非单调性偏离 2V 和 0.8V 的位置越远越好,查询 SDRAM 数据手册,考虑过冲阈值的前提下,选取  $0\Omega$  端接电阻非单调性位置偏离未定态最远,满足 SDRAM 数据手册参数要求。

用高带宽示波器测量得到实际串联 0Ω 端接电阻下的时钟信号波形如图 8 所示。

由图 8 可知,当端接电阻阻值改为 0Ω 时,信号上升沿不单调区间发生在 2.53V 附近,信号下降沿不单调区间发生在 0.6V 附近,与仿真波形一致。在 0.8~2.0V 的未定态区间不存在信号上升沿或者下降沿不单调的情况,可以避免时钟信号电平误判。

为了验证仿真模型的正确性,将端接电阻  $R_1$  改为  $16\Omega$  和  $33\Omega$ ,测量得到 ECLKOUT 管脚信号 波形如图 9、图 10 所示。

图 8 装配 0Ω 端接电阻时 ECLKOUT 信号 Fig. 8 Measurement waveform of ECLKOUT signal with 0Ω resistance

图 9 装配 16Ω端接电阻时 ECLKOUT 信号 Fig. 9 Measurement waveform of ECLKOUT signal with 16Ω resistance

图 10 装配 33Ω 端接电阻时 ECLKOUT 信号 Fig. 10 Measurement waveform of ECLKOUT signal with 33Ω resistance

测量结果同样显示,信号上升沿不单调的位置随着端接电阻阻值的变小而逐步提高,将端接电阻换成  $0\Omega$  后非单调性的位置最高,改成  $16\Omega$  和  $33\Omega$  时过冲较小,但非单调性的位置较低。将产品中端接电阻由  $22\Omega$  更改为  $0\Omega$ ,单板进行一40° ~ 70° 范围内的变温试验验证,温度变化速率为不大于 2° C/min。温度变化过程中,连接仿真器,配置 DSP 参数后,加载 SDRAM 测试程序,对 SDRAM 每个地址分别写入 0×55555、0×AAAAA 和 0  $\sim$  0×FFFF 递加三种数据。然后对读出和写入数据进行比较,测试过程中读出写入数据次数大于  $1 \times 10^8$  次,未发现读出写入数据不符的情况。

由上述分析和测试可知,去除  $R_1$  端接电阻, ECLKOUT 信号完整性能够满足器件要求。但值得注意的是,去除  $R_1$  端接电阻,虽然使得信号非单调性处的电压不处于未定态区间,但端接电阻过小会使得信号的过冲加大,过大的过冲可能导致芯片损坏或者影响芯片的使用寿命。此时要将过冲控制在相应的总线规范和芯片数据手册中规定的限定值内,在后续设计中应在 PCB 投产之前进行阻抗匹配和拓扑结构等方面的综合设计,完成信号完整性仿真,以确定最优的设计方案和参数。

## 4 结论

本文以某导航计算机为例,运用信号完整性分析技术分析了传统经验设计下端接电阻阻值匹配不当引起的边沿非单调性问题。通过对导航计算机电路板进行信号完整性分析和测试,得到如下结论:1)端接电阻阻值选取不当会引起 SDRAM 的时钟信号的非单调性问题,造成数据读取异常;2)进行信号完整性仿真有助于在既定 PCB 布局下快速选取保证数据正常读取的最佳端接电阻阻值;3)仿真和实验结果表明,在正常的高速数字电路研制流程中,加入信号完整性仿真可以在不进行投产的情况下遍历所有取值情况,可以提前规避风险,有效缩短高速电路研制周期,降低研制成本。

#### 参考文献

- [1] 周忠山. DDR2 高速 PCB 设计与信号完整性[J]. 电子技术与软件工程, 2017(9):81.

- Zhou Zhongshan. DDR2 high speed PCB design and signal integrity[J]. Electronic Technology & Software Engineering, 2017(9);81(in Chinese).

- [2] 谢锐,裴东兴,姚琴琴. 高频信号动态测试中的信号

完整性分析[J]. 仪器仪表学报,2017,38(3):773-779.

Xie Rui, Pei Dongxing, Yao Qinqin. Signal integrity analysis in high-frequency signal dynamic test[J]. Chinese Journal of Scientific Instrument, 2017, 38 (3):773-779(in Chinese).

- [3] 吴金玲. 基于 DSP 技术的导航计算机数据处理系统 研究[J]. 电子设计工程, 2018, 26(7):59-62.

- Wu Jinling. Research on navigation computer data processing system based on DSP technology[J]. Electronic Design Engineering, 2018, 26 (7): 59-62 (in Chinese).

- [4] 缑丽敏, 刘陶, 刘良勇. 基于 DSP 和 FPGA 技术的导航计算机设计与实现[J]. 电脑知识与技术, 2017, 13(2):218-219.

- Gou Limin, Liu Tao, Liu Liangyong. Design and implementation of navigation computer based on DSP and FPGA technology[J]. Computer Knowledge and Technology, 2017, 13(2):218-219(in Chinese).

- [5] 赵振涌,袁寰. 高精度 A/D 转换技术在惯导系统中的应用研究[J]. 导航定位与授时,2014,1(2):70-73.

- Zhao Zhenyong, Yuan Huan. Research on high accuracy analog-to-digital convert for inertial navigation systems [J]. Navigation Positioning and Timing, 2014,1(2): 70-73(in Chinese).

- [6] 刘旭东. DSP 技术下导航计算机数据处理系统设计与实现[J]. 山东工业技术, 2017(16):169. Liu Xudong. Design and implementation of navigation computer data processing system based on DSP technology[J]. Shandong Industrial Technology, 2017 (16):169(in Chinese).

- [7] Wu Jinling. Research on navigation computer data processing system based on DSP technology[J]. Electronic Design Engineering, 2018.

- [8] 张敏. 高速并行总线接口信号的完整性及设计优化 [J]. 无线互联科技,2018,15(6):3-4.

Zhang Min. Signal integrity and design optimization of high speed parallel bus interface[J]. Wireless Internet Technology,2018,15(6):3-4(in Chinese).

- [9] 陈治洲,曹开钦,柴孟阳,等.基于SRAM 乒乓缓存信号完整性分析[J].现代电子技术,2018,41(5):83-88.

- Chen Zhizhou, Cao Kaiqin, Chai Mengyang, et al. Signal integrity analysis based on ping-pong buffer circuit of SRAM[J]. Modern Electronics Technique, 2018, 41(5): 83-88(in Chinese).

- [10] 肖成.双 DSP 为核心导航计算机的模块化设计[J].

菏泽学院学报,2017,39(5):50-54.

Xiao Cheng. On modular design of navigation computer with double DSP[J]. Journal of Heze University, 2017, 39(5);50-54(in Chinese).

[11] 朱园园. 高速电路设计中的信号完整性研究[J]. 电子技术与软件工程,2015(20):36.

Zhu Yuanyuan. Signal integrity research in high speed circuit design[J]. Electronic Technology & Software

Engineering, 2015(20):36(in Chinese).

- [12] 金帅, 韩连刚, 谢锡海. DDR3 与 FPGA 接口的高速 电路板信号完整性分析[J]. 现代电子技术, 2017, 40(22):10-13. Jin Shuai, Han Liangang, Xie Xihai. Signal integrity analysis of high-speed circuit board interconnecting DDR3 and FPGA[J]. Modern Electronics Technique, 2017, 40(22):10-13(in Chinese).

- [13] Lu T, Sun J, Wu K, et al. High-speed channel modeling with machine learning methods for signal integrity analysis[J]. IEEE Transactions on Electromagnetic Compatibility, 2018(99):1-8.

- [14] 邓素辉, 谭子诚, 鄢秋荣, 等. 基于 Cadence 软件高速 PCB设计的信号完整性仿真[J]. 实验室研究与探索, 2017(12):116-120.

Deng Suhui, Tan Zicheng, Yan Qiurong, et al. Signal integrity simulation in the design of the high speed PCB by using Cadence software[J]. Research and Exploration in Laboratory, 2017(12):116-120(in

Chinese).

- [15] 王圣俊,柴小丽,颜爱良. 双存储控制系统中高速信号完整性设计[J]. 电子设计工程,2018,26(4):114-121.

- Wang Shengjun, Chai Xiaoli, Yan Ailiang. High-speed signal integrity design in gual storage control system[J]. Electronic Design Engineering, 2018, 26(4):114-121(in Chinese).

- [16] 缑新科,王妮儿,任崇玉. PCB 参数对 LPDDR3 信号完整性的影响[J]. 兰州理工大学学报,2017,43 (2):92-96.

- Gou Xinke, Wang Nier, Ren Chongyu. Influence of PCB parameters signal integrity of LPDDR3 [J]. Journal of Lanzhou University of Technology, 2017, 43(2): 92-96(in Chinese).

- [17] 周路, 贾宝富. 信号上升或下降时间对高速电路信号完整性影响的研究[J]. 现代电子技术, 2011, 34 (6): 69-73.

- Zhou Lu, Jia Baofu. Effects of signal rise or fall time on high-speed circuits signal integrity[J]. Modern Electronics Technique, 2011, 34 (6): 69-73 (in Chinese).

- [18] Wang S, Xu X, Zhou G, et al. Effects of microstrip line fabrication and design on high-speed signal integrity transmission of PCB manufacturing process[J]. Circuit World, 2018, 44(2): 53-59.